lspci -v

00:00.0 Bridge: Xilinx Corporation Device d011

Flags: fast devsel, IRQ 255

Bus: primary=00, secondary=01, subordinate=0c, sec-latency=0

I/O behind bridge: 00000000-00000fff [size=4K]

Memory behind bridge: None

Prefetchable memory behind bridge: None

Capabilities: [40] Power Management version 3

Capabilities: [60] Express Root Port (Slot-), MSI 00

Capabilities: [100] Device Serial Number 00-00-00-00-00-00-00-00

Capabilities: [10c] Virtual Channel

Capabilities: [128] Vendor Specific Information: ID=1234 Rev=1 Len=018 <?>

Host用的Avnet的FPGA,

M.2 接口插入RM500Q启动到内核后lspci认不出设备。

同样的方法Sierra社的卡可以认出来。

驱动用的这个

Quectel_Linux_PCIE_MHI_Driver_V1.3.1

如果在Linux使用的话还需要什么别的软件进行控制么?

同RM500Q一张卡放在评价版上USB连接可以认出来/也能通信。

追記:

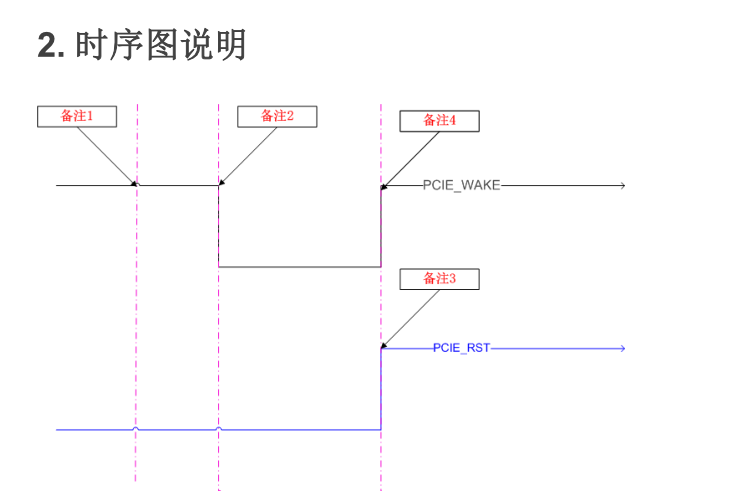

这个和向PCIE提供的信号相关么?

这边用的是LVDS 而没有使用HCSL。